Energy Efficiency

(Thrust leader: Ali Niknejad, UC Berkeley)

The TxACE Energy and Efficiency thrust encompasses cross-cutting research tackling energy efficiency in electronic systems, spanning from advanced power management, all the way to the emerging fields of low power machine learning/AI for edge computing and applications to IoT sensor nodes. The power management research forms the foundation of the center and tackles important issues of efficiency in complex system applications, for example in digital multi-core systems that use single inductor multiple output (SIMO) DC-DC converters, addressing modeling and simulation and optimization of performance (transient response, EMI, security) using non-linear computational control, mixed- signal techniques, digital signal processing, and adaptive algorithms and design automation. This thrust investigates non-conventional hybrid architectures and integration strategies for applications in computing, large-ratio conversion from 48V down to 1V and below, and charging applications. Many of the solutions employ mixed-signal techniques, exploiting advanced CMOS digital nodes alongside GaN power devices, and utilize novel scaling-friendly analog architectures to improve the control and expand the flexibility of the overall system.

Energy Efficiency Thrust

| Category | Accomplishment |

|---|---|

| Energy Efficiency (Systems) | Search for a middle ground between in-memory computation with conventional digital techniques and programmable accelerators for deep neural networks (DNN), particularly at the Edge such as in IoT applications has led to demonstration of a 28-nm CMOS prototype achieving 3.1 µJ-per-inference (with 90.2% accuracy) on the CIFAR-10 benchmark, as well as commensurate energy savings on all standard tinyML application benchmarks. The key is a processing element (PE) array that intersperses partial product accumulation circuitry with local SRAM kernel storage and digital multipliers, allowing fully unrolled and pipelined operations which reduces the activation memory needed and eliminates hardware, and reduces activation access. (2810.078, B. Murmann, Stanford University) |

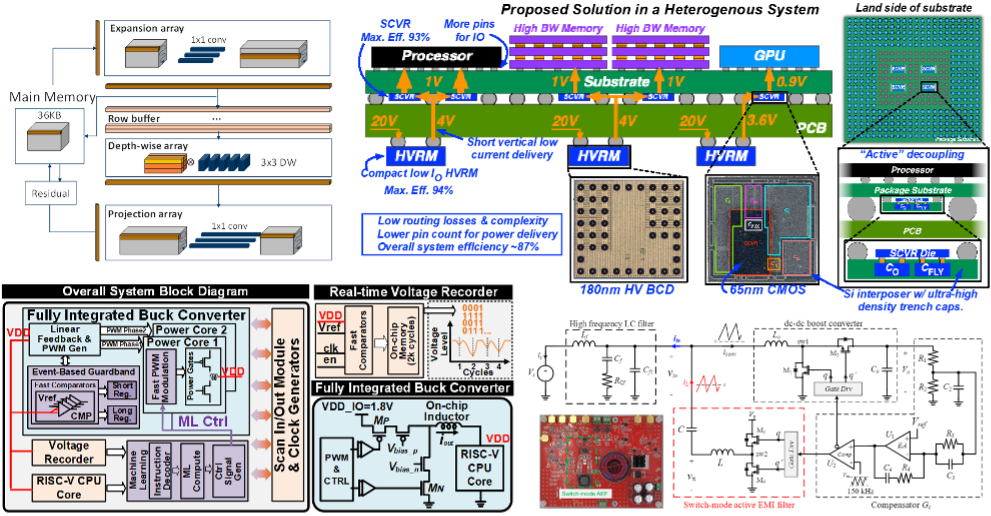

| Energy Efficiency (Circuits) | Efficiency of power delivery from high-voltage busses to scaled-CMOS-compatible voltages (<1V) is improved by ~10% employing a vertically and heterogeneously integrated architecture leveraging hybrid and switched-capacitor DC-DC converters. This architecture also reduces the number of power pins by at least 2x and reduces thermal dissipation. The SCVR was implemented in a 65-nm CMOS process, while the HVRM in a 180-nm BCD process. (2810.061, H. Le, University of California, San Diego) |

| Energy Efficiency (Circuits) | A linear regression machine learning model is trained based on simulation of both digital core and power management circuitry capturing the relationship among CPU’s power consumption, supply droops, and CPU’s internal signals, e.g. Opcode. A machine learning core generates a prediction of the CPU current consumption 2~3 cycles early. The prediction is sent to the buck converter and combined with real-time measured supply voltage to deliver “feedforward” regulation to the incoming current surge. To deal with the inaccuracy of machine learning prediction, an event-based guard-band circuit is also included as the “safety net”. This proactive scheme achieves 6%~10% improvements on CPU frequency or converter efficiency. (2810.039, J. Gu, Northwestern University) |