### THE UNIVERSITY OF TEXAS AT DALLAS

ERIK JONSSON SCHOOL OF ENGINEERING AND COMPUTER SCIENCE

# **ANNUAL REPORT** 2022 – 2023

Semiconductor Research Corporation

## **TXACE MISSION**

The Texas Analog Center of Excellence seeks to create fundamental analog, mixed signal and RF design innovations in integrated circuits and systems that improve energy efficiency, health care, and public safety and security.

## **TXACE THRUSTS**

Safety, Security and Health Care

Energy Efficiency

Fundamental Analog Circuits

## TxACE 2022–2023 ANNUAL REPORT

The Texas Analog Center of Excellence (TxACE), located at the University of Texas at Dallas is the largest analog research center based in an academic institution. Analog and mixed signal integrated circuits engineering is both a major opportunity and challenge. Analog circuits are critical components of the majority of products for the \$550+ billion per year integrated circuits industry, providing sensing, actuation, communication, power management and other functions. Digital integrated circuits such as microprocessors, logic circuits and memories are now integrating analog functions such as input/output circuits, phase locked loops, temperature sensors and power management circuits. It is also common to find microcontrollers with multiple analog-to-digital and digital-to-analog converters. These circuitries impact almost all aspect of modern life: safety security, health care, transportation, energy, entertainment and others.

Creation of advanced analog and mixed signal circuits and systems depends on the availability of engineering talent for analog research and development. TxACE was established to help translate the opportunity into economic benefits by overcoming the challenge and meeting the need through a collaboration of the state of Texas, Texas Instruments, the Semiconductor Research Corporation, the University of Texas System, and The University of Texas at Dallas.

The research tasks are organized into three research thrust areas: Safety, Security and Health Care, Energy Efficiency and Fundamental Analog. The scope of investigation extends from circuits operating at dc through terahertz, data converters that sample at a few samples/sec to 10's of Giga-samples/sec, AC-to-DC and DC-to-AC converters working at  $\mu$ W to Watts, energy harvesting circuits, sensors and many more. Significant improvements to existing mixed signal systems and new applications have been made and continued to be anticipated. Students who have been exposed to hands-on innovative research are forming the leading edge of analog talent flow into the industry. Close collaboration with and responsiveness to industry needs provide focus to the educational experience.

### DIRECTOR'S MESSAGE

The Texas Analog Center of Excellence (TxACE) is leading analog research and education. Over the past year, TxACE researchers published 24 journals, 59 conference papers and made 10 invited presentations. We also filed 9 patent applications and 2 invention disclosures. 3 patents were granted. 37 Ph.D., 8 M.S., and 2 B.S. students have completed their degree program.

Last year, the Center funded 82 research tasks led by 73 principal investigators at 28 institutions, including three international universities in India, Taiwan, and Canada. The Center supported 215 graduate and undergraduate students.

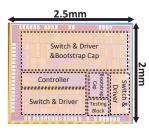

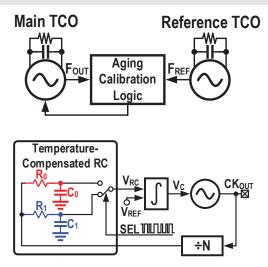

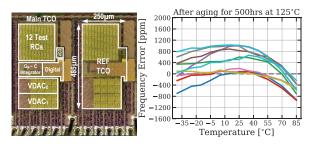

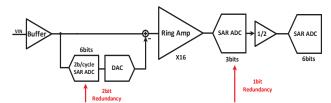

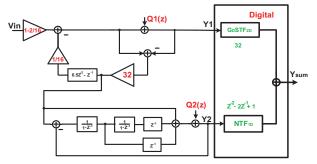

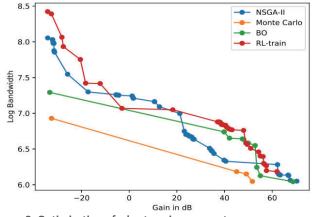

The Center is continuing to make impact to the industry and our way of life through its research accomplishments. There are always too many to list all. A partial list includes demonstration of a temperature- and agingcompensated RC Oscillator that achieves an inaccuracy of ±1030 ppm over -40°C to 85°C after 500 hours of accelerated aging at 125°C, improvement of efficiency of power delivery from high-voltage busses to scaled-CMOS-compatible voltages (<1V) by ~10% employing a vertically and heterogeneously integrated architecture leveraging hybrid and switched-capacitor DC-DC converters, capturing STEM images of p-GaN E-mode HEMTs with in-situ bias for electrical stress, a hybrid ADC in 28-nm CMOS that combines a VCO-based continuous-time delta-sigma modulator with a noise-shaping successive approximation register quantizer that achieves an 84.2-dB signal-to-noise-distortion ratio and an 86.8-dB dynamic range while consuming 1.62mW at 100MS/s, and a programmable accelerator for DNN in 28-nm CMOS for edge applications achieving 3.1 µJper-inference with 90.2% accuracy on the CIFAR-10 benchmark.

The TxACE laboratory is continuing to help advance integrated circuit research by making its instruments and expertise available to researchers and our industrial partners all over the world.

I am pleased to share the news that TxACE has been renewed by SRC for another three years with a total support of \$19.3 Million. I would like to thank UT Dallas, the University of Texas System, TI, and SRC, as well as many friends of TxACE all over the world for their generous support. Lastly, I would like to thank the students, principal investigators and staff for their efforts, and I look forward to another year of working with the TxACE team to make our way of life better, safer, healthier and more energy efficient through our research, education and innovation.

Kenneth K. O, Director TxACE Texas Instruments Distinguished University Chair Professor The University of Texas at Dallas

### **BACKGROUND & VISION**

The \$550+ billion per year integrated circuits industry is evolving into an analog/digital mixed signal industry. Analog circuits are providing or supporting critical functions such as sensing, actuation, communication, power management and others. These circuits impact almost all aspect of modern life including safety, security, health care, transportation, energy, and entertainment. To lead this change, in particular to lead analog and mixed signal technology education, research, commercialization, manufacturing, and job creation, the Texas Analog Center of Excellence was announced by Texas Governor Rick Perry in October 2008 as a collaboration of the Semiconductor Research Corporation, state of Texas through its Texas Emerging Technology Fund, Texas Instruments Inc., University of Texas system and University of Texas at Dallas. The Center seeks to accomplish the objectives by creating fundamental analog, mixed signal and RF design innovations in integrated circuits and systems that improve energy efficiency, healthcare, and public safety and security as well as by improving the research and educational infrastructure.

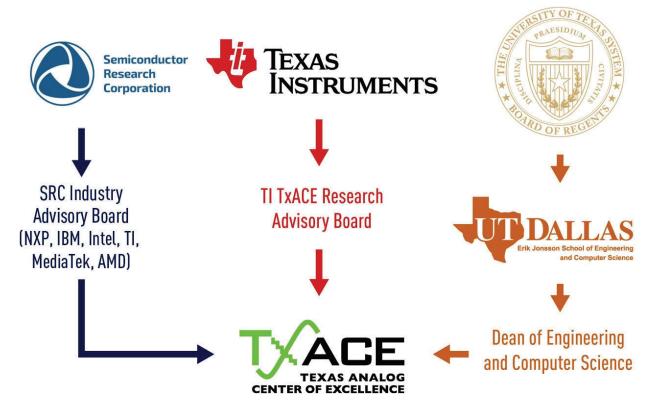

Figure 1. TxACE organization relative to the sponsoring collaboration.

### **CENTER ORGANIZATION**

The Texas Analog Center of Excellence is guided by agreements established with the Center sponsors. Members of the industrial advisory boards identify the research needs and select research tasks in consultation with the Center leadership. Figure 1 diagrams the relationship of TxACE to the members of the sponsoring collaboration.

## The internal organization of the Center is structured to flexibly perform the research mission while fully embracing the educational missions of the Universities.

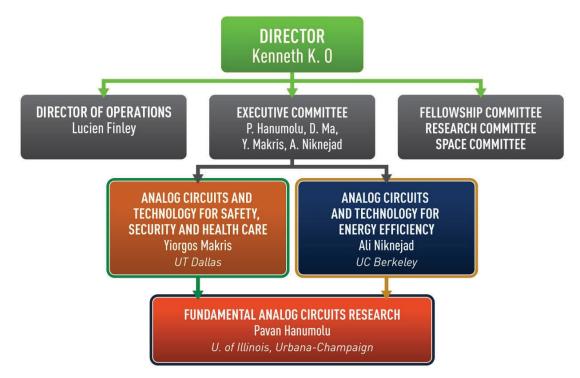

Figure 2 shows the center management structure. The TxACE Director is Professor Kenneth O. The research is arranged into three thrusts that comply with the center mission: Safety, Security and Health Care, Energy Efficiency and Fundamental Analog Research. The third thrust consists of vital research that cuts across the first two research thrusts. The thrust leaders are Prof. Yiorgos Makris of the University of Texas at Dallas for safety, security and health care, and Prof. Ali Niknejad of the University of California, Berkeley for energy efficiency. The leader for fundamental analog is Prof. Pavan Hanumolu of University of Illinois, Urbana-Champaign. The thrust leaders along with Professor Dongsheng Ma of The University of Texas at Dallas form the executive committee. The committee, along with the director, forms the leadership team that works to improve the research productivity by increasing collaboration, better leveraging the diverse capabilities of principle investigators of the Center, and lowering research barriers. The leadership team also identifies new research opportunities for consideration by the Industrial Advisory Boards.

Figure 2. TxACE organization for management of research

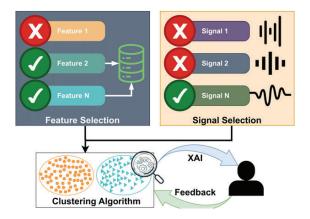

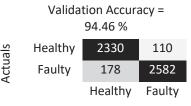

### SAFETY, SECURITY & HEALTH CARE

(Thrust leader: Yiorgos Makris, University of Texas at Dallas)

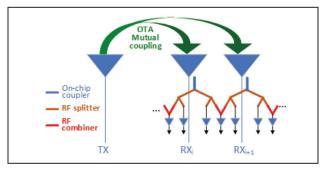

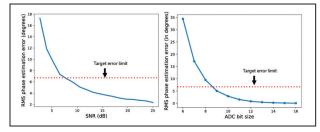

The efforts in the Safety, Security, and Health care thrust focus on improving safety by mitigating various reliability threats in analog/RF devices, including manufacturing defects, process variation, ESD and thermal degradation, as well as by developing effective machine learning-based design, verification and self-test solutions for mixed-signal automotive ICs. Particular emphasis has been placed on characterizing circuit aging, predicting failures and increasing lifetime of nano-scale CMOS circuits. An array of approaches is being developed for infield detection and localization of both hard and soft analog faults, as well as for low-cost design, test and calibration of RF MIMO systems. Machine learning assisted Design-for-Test solutions as well as inductive fault analysis schemes for statistically characterizing effectiveness of test suites through analog test metrics are also being developed for analog/RF ICs, including DACs. Additionally, this thrust investigates G-Band CMOS mmWave imagers and sensors for biomedical applications and IR gas sensors, as well as methods for analyzing reliability and monitoring the condition of GaN HEMTs. Lastly, this thrust investigates methods for motor health monitoring, laser systems for creating single-event effects that can be used to study radiation tolerance, as well as efficient temperature sensors for thermal performance characterization in power ICs.

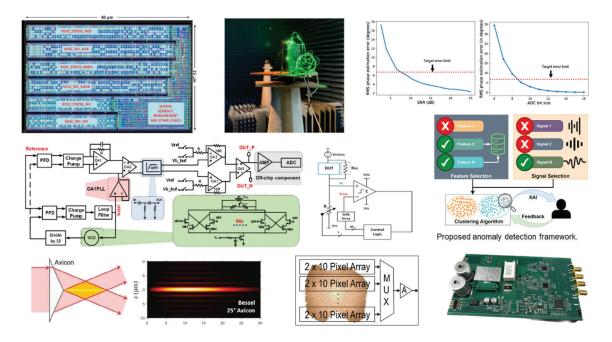

Figure 3. (Top left) Automatically generated layout of 12-nm LVT odometer (C. Kim, University of Minnesota), (Top right) Setup for error measurements in RF MIMO systems (S. Ozev, University of Arizona). (Middle left) PLL incorporating a 4-GHz VCO, array of cross-coupled NMOS transistors and circuits for on-chip phase noise measurements (K. O, University of Texas at Dallas). (Middle center) TDDB ageing sensor (D. Chen, University of Iowa). (Middle right) Anomaly detection framework for automotive ICs (K. Basu, University of Texas at Dallas). (Bottom left) Axicon lens creating Bessel laser beam mimicking heavy ion event distribution (R. Baumann, University of Texas at Dallas). (Bottom center) Array of 200 SRR-based pixels for 2D biological sample imaging (A. Niknejad, University of California, Berkeley). (Bottom right) Setup for transient reliability and condition monitoring of GaN HEMTs (B. Akin, University of Texas at Dallas).

### **ENERGY EFFICIENCY**

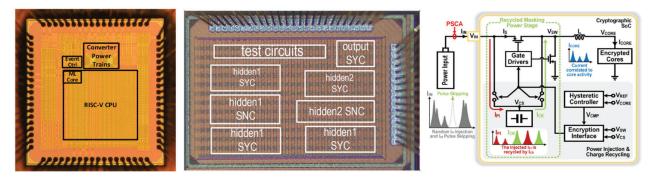

(Thrust leader: Ali Niknejad, UC Berkeley)

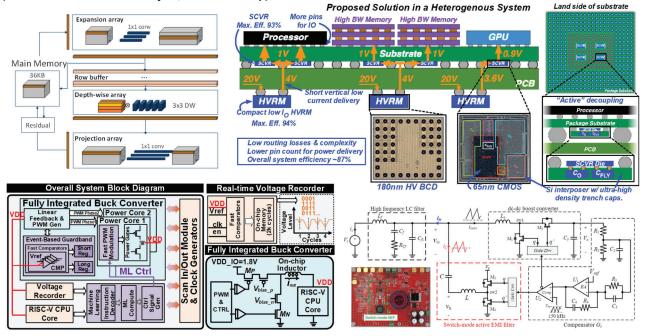

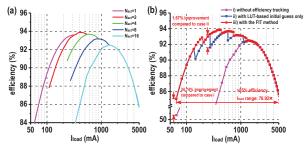

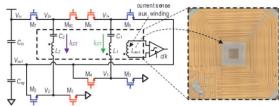

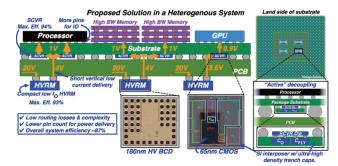

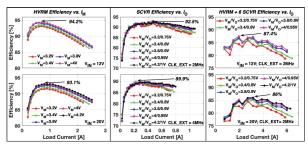

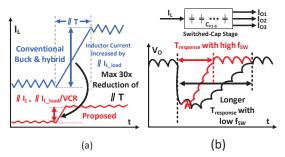

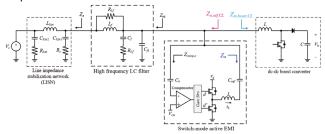

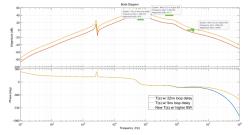

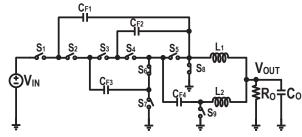

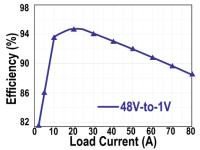

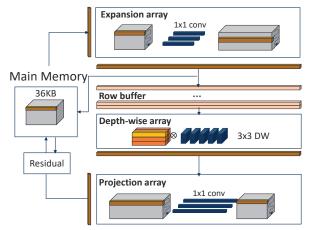

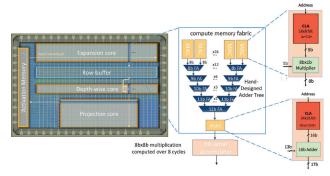

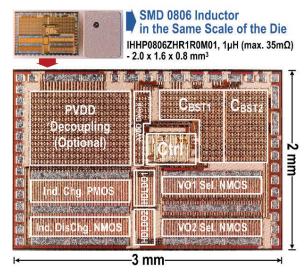

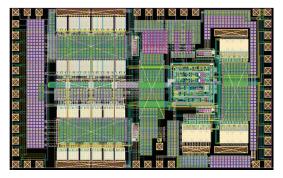

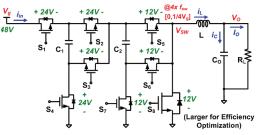

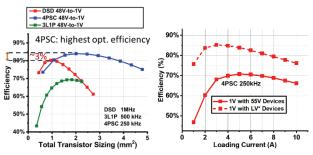

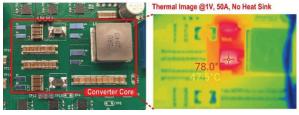

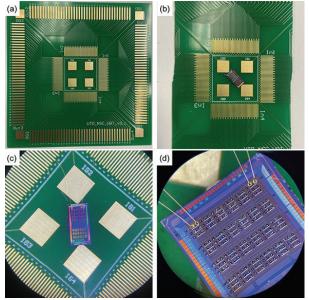

Figure 4. The TxACE Energy Efficiency thrust has diverse tasks ranging from advanced power management to digital and analog mixed-signal AI/ML for sensors and IoT systems, spanning a power range all the way from automotive kilowatts to always-on sensor systems consuming microwatts. (Top left) Pipelined machine learning processor architecture for bottleneck layers employed in a 28-nm CMOS prototype achieving 0.83/2.7 µJ/Frame for 86%/90.6% on CIFAR-10 (B. Murmann, Stanford University). (Top right) The two-stage vertical power delivery architecture for 20Vto-1V conversion, VPD-1 including an HVRM and an iPD + SCVR. The heterogeneous integrated PD system prototype achieves ~10% higher peak system efficiency than the state of the art (H. Le, University of California, San Diego). (Bottom, left) Architecture of a test chip that uses predicted voltage based on the CPU operating conditions from a machine learning core to modify the PWM control signal of a buck converter for regulating supply droop (J. Gu, Northwestern University). (Bottom, right) Active EMI filtering uses closed-loop control to sink/source a copy of the power converter ripple current. The amplifier is typically a linear amplifier, which incurs high loss if it must handle large ripple currents, instead a switch-mode amplifier is employed. A prototype demonstrates more than 40 dB of ripple attenuation at 1/8 the volume of a conventional LC filter (A. Hanson, University of Texas, Austin)

The TxACE Energy and Efficiency thrust encompasses cross-cutting research tackling energy efficiency in electronic systems, spanning from advanced power management, all the way to the emerging fields of low power machine learning/AI for edge computing and applications to IoT sensor nodes. The power management research forms the foundation of the center and tackles important issues of efficiency in complex system applications, for example in digital multi-core systems that use single inductor multiple output (SIMO) DC-DC converters, addressing modeling and simulation and optimization of performance (transient response, EMI, security) using non-linear computational control, mixed-signal techniques, digital signal processing, and adaptive algorithms and design automation. This thrust investigates non-conventional hybrid architectures and integration strategies for applications in computing, large-ratio conversion from 48V down to 1V and below, and charging applications. Many of the solutions employ mixed-signal techniques, exploiting advanced CMOS digital nodes alongside GaN power devices, and utilize novel scaling friendly analog architectures to improve the control and expand the flexibility of the overall system.

### FUNDAMENTAL ANALOG CIRCUITS RESEARCH

(Thrust leader: Pavan Hanumolu, U. of Illinois Urbana-Champaign)

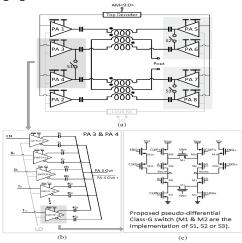

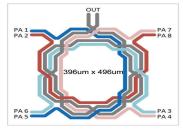

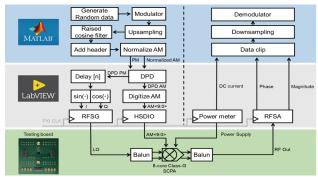

The research in this thrust focuses on cross-cutting areas in analog and mixed-signal circuits, which impact all TxACE application areas (Energy Efficiency, Public Safety, Security, and Health Care). The research includes the design of various analog-to-digital converters, communication links, low-power crystal oscillators, on-chip frequency references, I/O circuits, noise reduction techniques, new amplifier topologies suitable for use in nano-scale CMOS, development of CAD tools for automatic design, layout generation, and testing of integrated circuits.

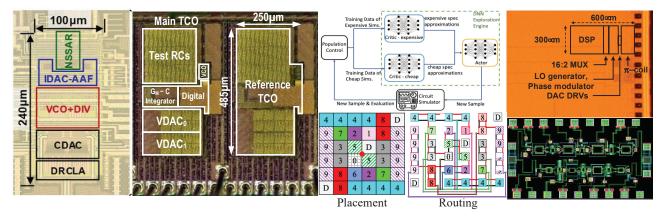

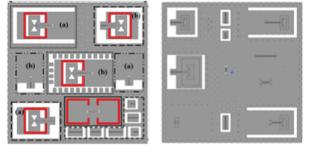

Figure 5. (Left) Noise-shaping SAR ADC (M. Flynn, University of Michigan). (Left middle) aging-compensated RC-based frequency reference (P. Hanumolu, University of Illinois Urbana-Champaign). (Top, right middle) DNN-based exploration engine used in layout-aware analog synthesis (D. Pan, University of Texas, Austin). (Top, right) multi-carrier DAC-based transmitter (S. Palermo, Texas A&M University). (Bottom, right middle) Placement and routing for an 8-bit split DAC (S. Sapatnekar, University of Minnesota). (Bottom, right) bi-directional PA-LNA (H. Wang, National Taiwan University).

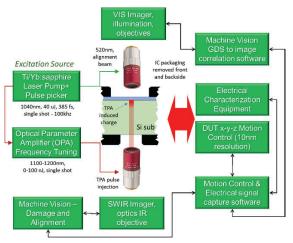

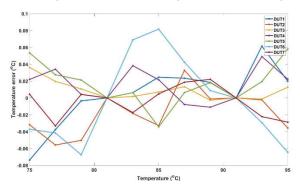

### **TXACE ANALOG RESEARCH FACILITY**

The centralized group of laboratories of the Texas Analog Center of Excellence dedicated to analog engineering research and training occupy a ~ 8000-ft<sup>2</sup> area on the 3rd floor of the Engineering and Computer Science North building (Figure 6). The facility includes RF and THz, Integrated System Design, Embedded Signal Processing, and Analog & Mixed Signal laboratories as well as CAD/Design laboratory structured to promote collaborative research. The unique instrumentation capability includes network analyses and linearity measurements up to 325 GHz, spectrum analysis up to 120 THz, and cryo-measurements down to 2°K. The Center also added a pulsed multiple harmonic load and source pull measurement set up (up to 60 GHz for the third harmonic) and a 325-GHz antenna measurement set up. The close proximity of researchers in an open layout enables natural interaction and compels sharing of knowledge and instrumentation among the students and faculty. The TxACE analog research facility is one of the best equipped electronics laboratories. The laboratory is available for use by TxACE researchers and industrial partners all over the world.

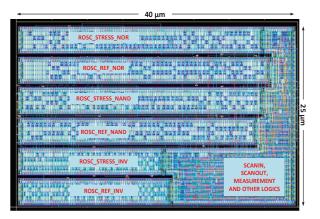

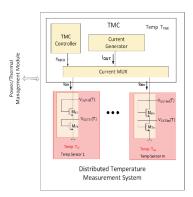

Figure 6. TxACE Analog Research Facility

### **RESEARCH PROJECTS AND INVESTIGATORS**

The Texas Analog Center of Excellence (TxACE) is the largest university analog technology center in the world. Table 1 lists the current principal investigators of the 82 tasks from 28 academic institutions funded by TxACE. Four universities (SMU, Texas A&M, UT Austin, UT Dallas) are from the state of Texas. 24 are from outside of Texas. Three (Indian Institute of Tech. Kharagpur, National Taiwan University, and University of Toronto) (Figure 7) are from outside of the US. Of the 73 investigators, 25 are from Texas. During the past year, the Center supported 164 Ph.D., 29 M.S., and 22 B.S. students. 37 Ph.D., 8 M.S., and 2 B.S. degrees were awarded to the TxACE students.

| Investigator  | Institution                            | Investigator | Institution                            | Investigator         | Institution      |

|---------------|----------------------------------------|--------------|----------------------------------------|----------------------|------------------|

| B. Akin       | UT Dallas                              | A. Hazra     | Indian Institute of<br>Tech. Kharagpur | B. Murmann           | Stanford         |

| N. Al-Dhahir  | UT Dallas                              | R. Henderson | UT/Dallas                              | F. Najm              | U Toronto        |

| D. Allstot    | Oregon State                           | D. Heo       | Washington State                       | A. Niknejad          | UC Berkeley      |

| A. Babakhani  | UCLA                                   | S. Hoyos     | Texas A&M                              | К. О                 | UT Dallas        |

| B. Bakkaloglu | Arizona State                          | C. Huang     | lowa State                             | S. Ozev              | Arizona State    |

| K. Basu       | UT Dallas                              | T. Huang     | National Taiwan                        | S. Palermo           | Texas A&M        |

| R. Baumann    | UT Dallas                              | Y. Jia       | UT Austin                              | D. Pan               | UT Austin        |

| D. Blaauw     | U Michigan                             | Y. Kaneda    | U Arizona                              | P. Pande             | Washington State |

| A. Chatterjee | Georgia Tech                           | C. Kim       | U Minnesota                            | M. Quevedo-<br>Lopez | UT Dallas        |

| D. Chen       | Iowa State                             | M. Kim       | UT Dallas                              | G. Rincón-Mora       | Georgia Tech     |

| S. Chen       | USC                                    | J. Kulkarni  | UT Austin                              | R. Rohrer            | SMU              |

| Y. Chiu       | UT Dallas                              | H. Le        | UCSD                                   | E. Rosenbaum         | UIUC             |

| P. Dasgupta   | Indian Institute of<br>Tech. Kharagpur | H. Lee       | UT Dallas                              | S. Sapatnekar        | U Minnesota      |

| J. Doppa      | Washington State                       | M. Lee       | UT Dallas                              | V. Sathe             | U Washington     |

| M. Flynn      | U Michigan                             | T. Levi      | USC                                    | M. Seok              | Columbia         |

| J. Friedman   | UT Dallas                              | P. Li        | UCSB                                   | H. Shichijo          | UT Dallas        |

| H. Fu         | Iowa State                             | K. Lin       | National Taiwan                        | J. Stauth            | Dartmouth        |

| I. Galton     | UCSD                                   | J. Liu       | UT Dallas                              | D. Sylvester         | U Michigan       |

| R. Geiger     | Iowa State                             | H. Lu        | UT Dallas                              | Y. Takashima         | U Arizona        |

| S. Gómez-Díaz | UC Davis                               | D. Ma        | UT Dallas                              | M. Torlak            | UT Dallas        |

| J. Gu         | Northwestern                           | N. Maghari   | U Florida                              | G. Trichopoulos      | Arizona State    |

### Table 1. Principal Investigators (May 2022 through April 2023)

| Investigator        | Institution | Investigator    | Institution  | Investigator | Institution     |

|---------------------|-------------|-----------------|--------------|--------------|-----------------|

| S. Gupta            | USC         | Y. Makris       | UT Dallas    | H. Wang      | National Taiwan |

| A. Hanson UT Austin |             | P. Mercier      | UCSD         | D. Wentzloff | U Michigan      |

| P. Hanumolu         | UIUC        | U. Moon         | Oregon State |              |                 |

| R. Harjani          | U Minnesota | S. Mukhopadhyay | Georgia Tech |              |                 |

Figure 7. Member Institutions of Texas Analog Center of Excellence

### SUMMARY OF RESEARCH PROJECTS

The 82 research projects funded through TxACE during 2022-2023 are listed in Table 2 below by the Semiconductor Research Corporation task identification number.

## Table 2: Funded research projects at TxACE by SRC task identification number (FA: Fundamental Analog, EE: Energy Efficiency, SS: Safety, Security and Health Care)

|    | Task                      | Thrust | Title                                                                                                                   | Task Leader                       | Institution                               |

|----|---------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------------------------|

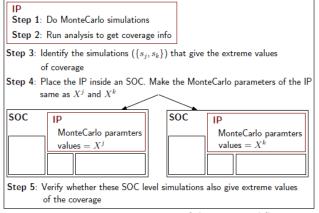

| 1  | 2810.019                  | FA     | Design Automation for Coverage Management in<br>Analog and Mixed-Signal SOCs                                            | Dasgupta, Pallab<br>Hazra, Aritra | Indian Institute<br>of Tech.<br>Kharagpur |

| 2  | 2810.028                  | FA     | Robust ATE Multi-Site HW Design to Enable<br>Effective Analog Performance Testing in Analog-<br>Mixed-Signal (AMS) SoCs | Chen, Degang                      | Iowa State                                |

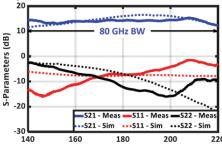

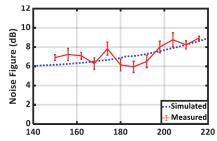

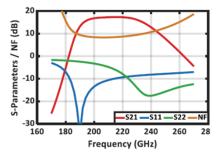

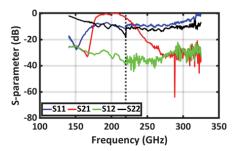

| 3  | 2810.029                  | FA     | 170GHz – 260GHz Wideband PA and LNA Design in<br>Silicon                                                                | Babakhani, Aydin                  | UC Los Angeles                            |

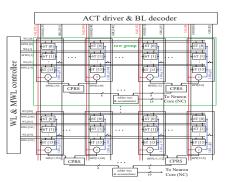

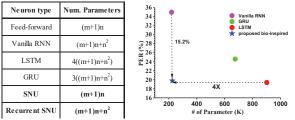

| 4  | 2810.030                  | FA     | Neural Network Recognition & On-Chip Online<br>Learning with STT-MRAM                                                   | Friedman, Joseph                  | UT Dallas                                 |

| 5  | 2810.032<br>&<br>3160.025 | EE     | DRIVR: A Digital, Re-configurable, Unified Clock-<br>Power (UNICAP) Fabric                                              | Sathe, Visvesh                    | Univ. of<br>Washington &<br>Georgia Tech  |

| 6  | 2810.033                  | FA     | Interleaved Noise-Shaping SAR ADCs for High-<br>Speed and High-Resolution                                               | Flynn, Michael                    | Univ. of<br>Michigan                      |

| 7  | 2810.034                  | EE     | Always-on Keyword Spotting based on Analog-<br>Mixed-Signal Computing Hardware                                          | Seok, Mingoo                      | Columbia                                  |

| 8  | 2810.035<br>&<br>3160.026 | EE     | Computationally Controlled Integrated Voltage<br>Regulators                                                             | Sathe, Visvesh                    | Univ. of<br>Washington &<br>Georgia Tech  |

| 9  | 2810.036                  | FA     | Highly Stable Integrated Frequency References                                                                           | Hanumolu, Pavan                   | UIUC                                      |

| 10 | 2810.037                  | FA     | High-performance Ringamp-based ADCs                                                                                     | Moon, Un-Ku                       | Oregon State                              |

| 11 | 2810.038                  | SS     | Extreme Temperature Digital, Analog, and Mixed-<br>Signal Circuits (ET-DAMS)                                            | Kim, Chris                        | Univ. of<br>Minnesota                     |

|    | Task     | Thrust | Title                                                                                                                                                      | Task Leader           | Institution           |

|----|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|

| 12 | 2810.039 | EE     | Development of Compact and Low Cost Fully<br>Integrated DC-DC Converter with Resonant Gate<br>Drive and Intelligent Transient Response                     | Gu, Jie               | Northwestern          |

| 13 | 2810.040 | EE     | Hybrid/Resonant Sc Converters with Integrated Lc<br>Resonator for High-Density Monolithic Power<br>Delivery                                                | Stauth, Jason         | Dartmouth<br>College  |

| 14 | 2810.041 | SS     | ESD Protection for IO Operating at 56 Gb/s and<br>Beyond                                                                                                   | Rosenbaum, Elyse      | UIUC                  |

| 15 | 2810.042 | EE     | Digitally Enhanced High Efficiency, Fast Settling<br>Augmented DCDC Converters                                                                             | Bakkaloglu, Bertan    | Arizona State         |

| 16 | 2810.043 | FA     | Analog Optimization Hybridizing Designer's Intent<br>and Machine Learning                                                                                  | Li, Peng              | UC Santa<br>Barbara   |

| 17 | 2810.044 | FA     | Hierarchical Characterization and Calibration of RF/Analog Circuits Using Lightweight Built-in Sensors                                                     | Ozev, Sule            | Arizona State         |

| 18 | 2810.046 | SS     | Generating Current Constraints for<br>Electromigration Safety                                                                                              | Najm, Farid           | Univ. of Toronto      |

| 19 | 2810.047 | SS     | Architecture and DfT methods for improving life<br>time reliability and functional safety of electronic<br>circuits and systems out of application context | Chen, Degang          | Iowa State            |

| 20 | 2810.048 | SS     | Characterization and Mitigation of<br>Electromigration Effects in Advanced Technology<br>Nodes                                                             | Kim, Chris            | Univ. of<br>Minnesota |

| 21 | 2810.049 | EE     | 1-W Battery-Charging CMOS Buck Regulator                                                                                                                   | Rincón-Mora, Gabriel  | Georgia Tech          |

| 22 | 2810.050 | SS     | Integrating Metasurfaces and MEMS for Gas<br>Sensing                                                                                                       | Gómez-Díaz, Sebastian | UC Davis              |

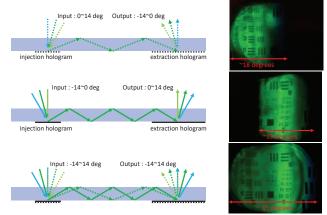

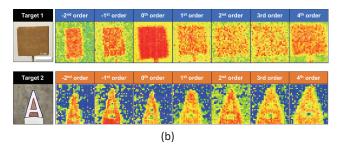

| 23 | 2810.052 | FA     | TI PLM as Hologram Generator for HUD and AR                                                                                                                | Kaneda, Yushi         | Univ. of Arizona      |

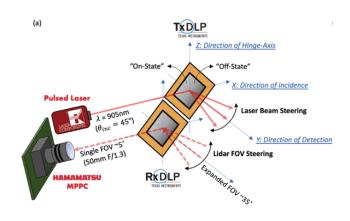

| 24 | 2810.053 | FA     | TI PLM to Advanced Lidar and Display Systems                                                                                                               | Takashima, Yuzuru     | Univ. of Arizona      |

| 25 | 2810.054 | SS     | Reconfigurable AC Power Cycling Setup and Plug-<br>in Condition Monitoring Tools for High Power IGBT<br>and SiC Modules                                    | Akin, Bilal           | UT Dallas             |

|    | Task     | Thrust | Title                                                                                                                                                             | Task Leader                                          | Institution          |

|----|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------|

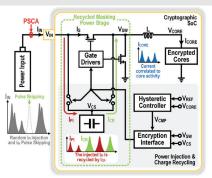

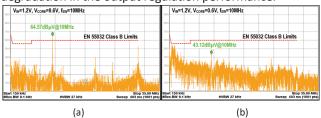

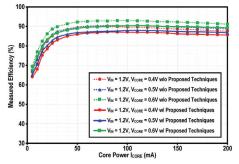

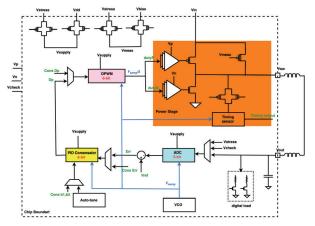

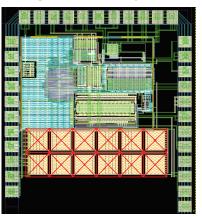

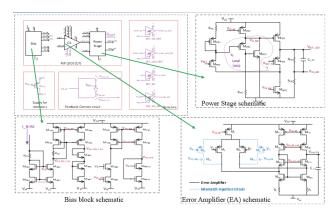

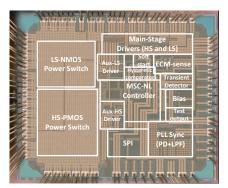

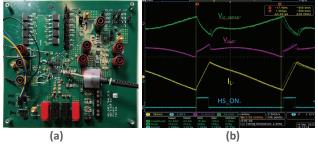

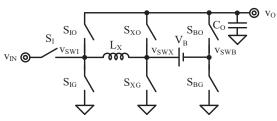

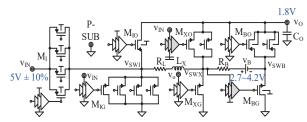

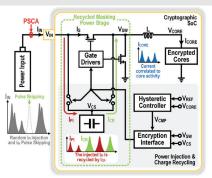

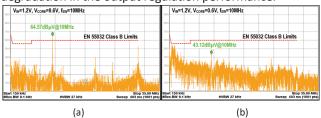

| 26 | 2810.055 | SS/EE  | EMI-Regulated Secure Automotive Power ICs                                                                                                                         | Ma, D. Brian                                         | UT Dallas            |

| 27 | 2810.056 | FA     | Millimeter Wave Packaging Research - Antenna in<br>Package                                                                                                        | Henderson, Rashaunda<br>Lee, Mark<br>Lu, Hongbing Lu | UT Dallas            |

| 28 | 2810.057 | SS     | Reliability Study of E-mode GaN HEMT Devices by<br>AC TDDB and High Resolution TEM                                                                                | Kim, Moon<br>Shichijo, Hishashi                      | UT Dallas            |

| 29 | 2810.058 | SS/FA  | Machine Learning-Based Overkill/Underkill<br>Reduction in Analog/RF IC Testing                                                                                    | Makris, Yiorgos                                      | UT Dallas            |

| 30 | 2810.059 | SS/EE  | Ultra-Low-Power Robust SAR ADC for PMCW<br>Automotive RADAR                                                                                                       | Chiu, Yun                                            | UT Dallas            |

| 31 | 2810.060 | FA     | Intelligent, Learning ADCs for the Post Figure-of-<br>Merit World                                                                                                 | Flynn, Michael                                       | Univ. of<br>Michigan |

| 32 | 2810.061 | EE     | Two-Stage Vertical Power Delivery and<br>Management for Efficient High-Performance<br>Computing                                                                   | Le, Hanh-Phuc<br>Mercier, Patrick                    | UC San Diego         |

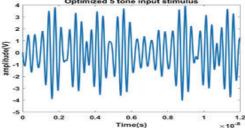

| 33 | 2810.062 | FA     | Multi-Carrier DAC-Based Transmitter<br>Architectures for 100+Gb/s Serial Links                                                                                    | Palermo, Samuel<br>Hoyos, Sebastian                  | Texas A&M            |

| 34 | 2810.063 | FA     | Analog and Digital Assist Techniques to Improve<br>Mixed-Signal Performance                                                                                       | Sylvester, Dennis<br>Blaauw, David                   | Univ. of<br>Michigan |

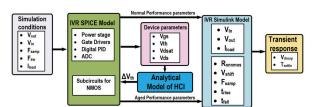

| 35 | 2810.064 | SS     | Characterization and Tolerance of Ageing in<br>Integrated Voltage Regulators                                                                                      | Mukhopadhyay, Saibal                                 | Georgia Tech         |

| 36 | 2810.065 | EE/SS  | Power-Efficient and Reliable 48-V DC-DC<br>Converter with Direct Signal-to-Feature Extraction<br>and DNN-Assisted Multi-Input Multiple-Output<br>Feedback Control | Seok, Mingoo                                         | Columbia             |

| 37 | 2810.066 | SS     | Demonstrably Generalizable Compact Models of<br>ESD Devices                                                                                                       | Rosenbaum, Elyse                                     | UIUC                 |

| 38 | 2810.067 | EE     | Highly Efficient Extreme-Conversion-Ratio Buck<br>Hybrid Converters                                                                                               | Pande, Partha<br>Heo, Deukhyoun<br>Doppa, Janardhan  | Washington<br>State  |

| 39 | 2810.068 | EE     | Active EMI Filtering with Switch-Mode Amplifier<br>for High Efficiency                                                                                            | Hanson, Alex                                         | UT Austin            |

|    | Task                      | Thrust | Title                                                                                                                                                  | Task Leader                           | Institution                 |

|----|---------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------|

| 40 | 2810.070                  | SS     | Early and Late Life Failure Prediction Methods for<br>Analog and Mixed-Signal Circuits                                                                 | Kim, Chris                            | Univ. of<br>Minnesota       |

| 41 | 2810.071                  | FA     | Accurate Compact Temperature Sensors for<br>Thermal Management of High Performance<br>Computing Platforms                                              | Geiger, Randall<br>Chen, Degang       | Iowa State                  |

| 42 | 2810.072<br>&<br>2810.073 | EE     | AI/ML Edge Hardware for Ultra-reliable Wireless<br>Networks                                                                                            | Allstot, David<br>Markis, Yiorgos     | Oregon State<br>& UT Dallas |

| 43 | 2810.074                  | SS     | Thermal Performance Characterization and<br>Degradation Monitoring of LDMOS based<br>Integrated Power IC with On-Die Temperature<br>Sensors            | Akin, Bilal                           | UT Dallas                   |

| 44 | 2810.075                  | EE     | Hybrid Step-Down DC-DC Converters with Large<br>Conversion Ratios for 48V Automotive<br>Applications                                                   | Lee, Hoi<br>Liu, Jin                  | UT Dallas                   |

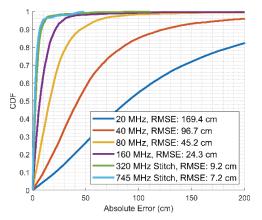

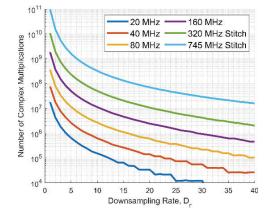

| 45 | 2810.076                  | FA     | High Precision Positioning Techniques Based onAl-Dhahir, NMultiple Technologies and Frequency BandsTorlak, Mu                                          |                                       | UT Dallas                   |

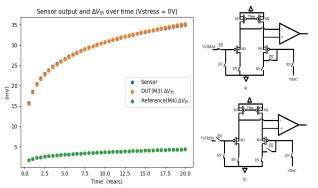

| 46 | 2810.077                  | SS     | Increasing Lifetime of Nano-Scale CMOS Circuits                                                                                                        | O, Kenneth                            | UT Dallas                   |

| 47 | 2810.078                  | EE     | Programmable Mixed-Signal Accelerator for DNNs with Depthwise Separable Convolution Layers                                                             | Murmann, Boris                        | Stanford                    |

| 48 | 2810.079                  | EE     | High-Power-Density In-Package SIMO Converters<br>for Next-Generation Microprocessors                                                                   | Huang, Cheng                          | Iowa State                  |

| 49 | 2810.080                  | EE     | Efficient and High-Density Fully In-Package GaN-<br>Based High-Ratio DC-DC Converters                                                                  | Huang, Cheng<br>Fu, Houqiang          | Iowa State                  |

| 50 | 2810.081                  | FA     | Wang, H<br>Development of 70-95 GHz Terabit Beamformer Huang, Tian<br>Lin, Kun-                                                                        |                                       | National Taiwan<br>Univ.    |

| 51 | 2810.082                  | FA     | Adaptive Digital Cancellation of Dynamic Error<br>from Clock Skew, Component Mismatches, and ISI<br>in High-Resolution RF DACs                         | Galton, lan                           | UC San Diego                |

| 52 | 2810.083                  | FA     | Automated Layout of Analog Arrays in Advanced<br>Technology Nodes                                                                                      | Sapatnekar, Sachin<br>Harjani, Ramesh | Univ. of<br>Minnesota       |

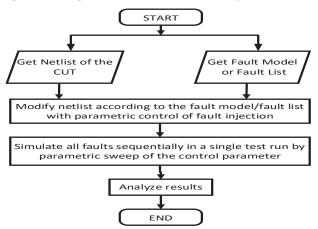

| 53 | 2810.084                  | SS     | Soft and hard analog fault detection, injection,<br>coverage, diagnosis, and localization strategies<br>suitable for production test and in-field test | Chen, Degang                          | Iowa State                  |

|    | Task     | Thrust | Title                                                                                                       | Task Leader                                    | Institution           |

|----|----------|--------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------|

| 54 | 2810.085 | FA     | Applications of Circuit Transient Sensitivity<br>Simulation to Semiconductor Circuit Analysis and<br>Design | Rohrer, Ronald                                 | SMU                   |

| 55 | 2810.086 | SS     | Machine Learning-based Functional Safety<br>Improvement of AMS components in Automotive<br>SoCs             | Basu, Kanad                                    | UT Dallas             |

| 56 | 2810.087 | EE     | Grid Optimization and Silicon Validation for Chip<br>Robustness                                             | Najm, Farid                                    | Univ. of Toronto      |

| 57 | 2810.088 | EE     | Grid Optimization and Silicon Validation for Chip<br>Robustness                                             | Kim, Chris                                     | Univ. of<br>Minnesota |

| 58 | 2810.089 | SS     | Techniques for Low-cost Design, Test, and<br>Calibration of RF MIMO Systems                                 | Ozev, Sule<br>Trichopoulos, Georgios           | Arizona State         |

| 59 | 2810.090 | SS     | Motor Health Monitoring                                                                                     | Akin, Bilal                                    | UT Dallas             |

| 60 | 2810.091 | SS     | Development of Two-Photon Absorption Laser<br>System for Creating Single Event Effects                      | Baumann, Robert &<br>Quevedo-Lopez,<br>Manuel  | UT Dallas             |

| 61 | 2810.092 | EE     | Battery-Charging CMOS Voltage Regulator for<br>Resistive Low-Voltage DC Sources                             | Rincón-Mora, Gabriel                           | Georgia Tech          |

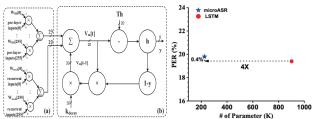

| 62 | 3160.002 | EE     | tinyASR: Self-Supervised, Sub-10μW Automatic<br>Speech Recognition Hardware for IoT Devices                 | Seok, Mingoo                                   | Columbia              |

| 63 | 3160.003 | SS     | Techniques for Online Ageing Detection and In-<br>field Characterization of Aging Phenomena                 | Chen, Degang                                   | Iowa State            |

| 64 | 3160.004 | SS     | Inductive Fault Analysis for Determining Statistical<br>Analog Test Metrics                                 | Ozev, Sule                                     | Arizona State         |

| 65 | 3160.005 | SS     | ML-Assisted Scalable DfT and BIST of AMS Systems                                                            | Chatterjee, Abhijit                            | Georgia Tech          |

| 66 | 3160.006 | FA     | Machine-Learning Based Analog Mixed-signal<br>Design Tool                                                   | Chen, Shuo-Wei<br>Gupta, Sandeep<br>Levi, Tony | USC                   |

| 67 | 3160.007 | FA     | AI-Assisted and Layout-Aware Analog Synthesis<br>and Optimization with Design Intent                        | Pan, David Z.<br>Jia, Yaoyao                   | UT Austin             |

|    | Task     | Thrust | Title                                                                                                  | Task Leader                                    | Institution           |

|----|----------|--------|--------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------|

| 68 | 3160.008 | FA     | High-Speed DAC with High Output Power and<br>Linearity                                                 | Chen, Shuo-Wei                                 | USC                   |

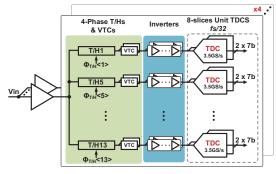

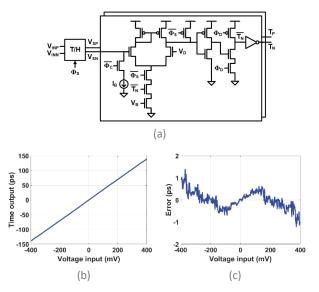

| 69 | 3160.009 | FA     | 100+GS/s Time-Domain Analog-to-Digital<br>Converters                                                   | Palermo, Samuel<br>Hoyos, Sebastian            | Texas A&M             |

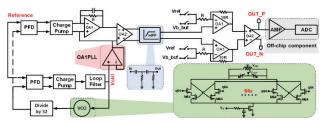

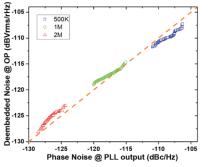

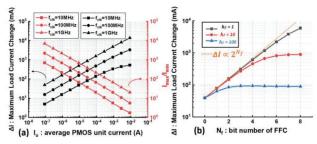

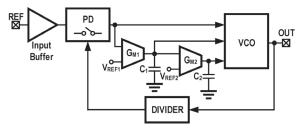

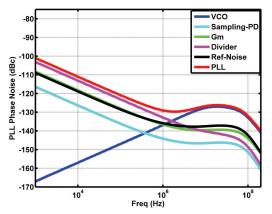

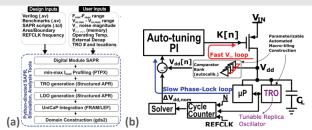

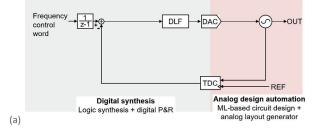

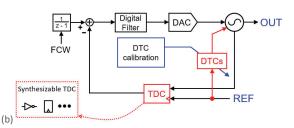

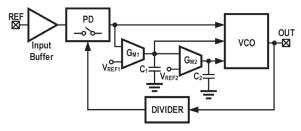

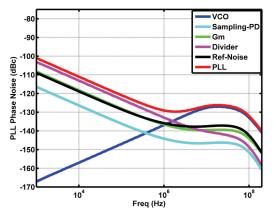

| 70 | 3160.010 | FA     | Design Automation of Low Phase Noise PLL                                                               | Chen, Shuo-Wei<br>Gupta, Sandeep<br>Levi, Tony | USC                   |

| 71 | 3160.011 | SS     | G-Band CMOS mm-Wave Imager and Sensor for<br>Biomedical Applications                                   | Niknejad, Ali                                  | UC Berkeley           |

| 72 | 3160.012 | SS     | Small-area Low-power DAC Designs with In-field<br>Digital Calibration Ensuring Lifetime High Linearity | Chen, Degang                                   | Iowa State            |

| 73 | 3160.013 | EE     | Energy-Efficient Circuits and Architectures for<br>Cryogenic Operation                                 | Kim, Chris                                     | Univ. of<br>Minnesota |

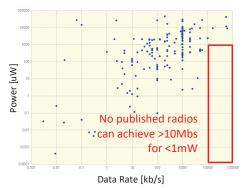

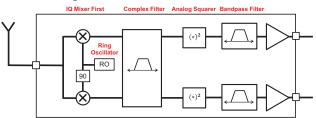

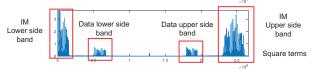

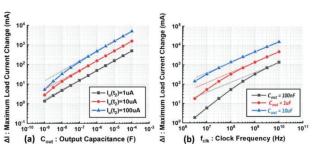

| 74 | 3160.015 | EE     | ULP Receivers                                                                                          | Wentzloff, David                               | Univ. of<br>Michigan  |

| 75 | 3160.016 | EE     | MODO: Hybrid SIMO-DLDO DC-DC Converter for<br>Multi-Core Microprocessors and System-on-Chips           | Seok, Mingoo                                   | Columbia              |

| 76 | 3160.017 | EE/FA  | Multi-phase Sub-100fs Jitter Ring-oscillator-based<br>Clock Multipliers for Beyond 100Gb/s Links       | Hanumolu, Pavan                                | UIUC                  |

| 77 | 3160.018 | FA     | Pseudo-Static Storage Circuits for Extreme Low<br>Voltage Cryo-CMOS Applications                       | Kulkarni, Jaydeep                              | UT Austin             |

| 78 | 3160.019 | FA     | Mixed-Domain High-Performance CT-ΔΣ ADCs                                                               | Maghari, Nima                                  | Univ. of Florida      |

| 79 | 3160.020 | SS     | Transient Reliability and Condition Monitoring of<br>GaN HEMTs                                         | Akin, Bilal                                    | UT Dallas             |

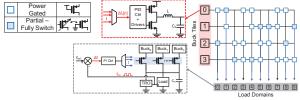

| 80 | 3160.021 | FA/EE  | Automated Generation of Comprehensive<br>Voltage/Frequency Domains - Logic+PLL+Voltage<br>Regulation   | Sathe, Visvesh                                 | Georgia Tech          |

| 81 | 3160.022 | EE     | Domain-Voltage Regulator Co-design for Enhanced<br>SoC Energy Efficiency                               | Sathe, Visvesh                                 | Georgia Tech          |

|    | Task     | Thrust | Title                                                                     | Task Leader          | Institution  |

|----|----------|--------|---------------------------------------------------------------------------|----------------------|--------------|

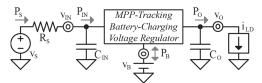

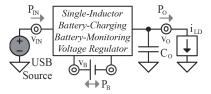

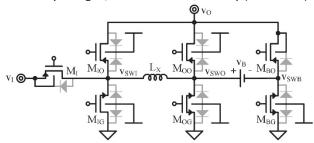

| 82 | 3160.024 | EE     | On-the-Go Battery Charging/Battery Monitoring<br>SIMIMO Voltage Regulator | Rincón-Mora, Gabriel | Georgia Tech |

### ACCOMPLISHMENTS

In the past year, TxACE has made significant research progress. Table 3 summarizes the number of publications and inventions resulting from the TxACE research during May 2022 to April 2023, while Table 4 lists the major research accomplishments for the Center during the period. The TxACE researchers have published 59 conference papers, 24 journal papers, and 10 Invited Presentations. The team also made 2 invention disclosures, filed 9 patent applications, and 3 patents were granted. The list of publications is included as Appendix I. Following the tabulation, brief summaries of each project are provided.

| Conference |                | Invited       | Invention   | Patents |                 |  |

|------------|----------------|---------------|-------------|---------|-----------------|--|

| Papers     | Journal Papers | Presentations | Disclosures | Filed   | Patents Granted |  |

| 59         | 24             | 10            | 2           | 9       | 3               |  |

### Table 3. TxACE number of publications (May 2022 through April 2023)

| Table 4 | . Major TxACE Research Accomplishments (May 2022 through April 2023) |

|---------|----------------------------------------------------------------------|

|         |                                                                      |

| Category                           | Accomplishment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

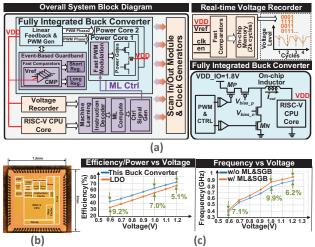

| Energy<br>Efficiency<br>(Systems)  | Search for a middle ground between in-memory computation with conventional digital techniques and programmable accelerators for deep neural networks (DNN), particularly at the Edge such as in IoT applications has led to demonstration of a 28-nm CMOS prototype achieving 3.1 µJ-per-inference (with 90.2% accuracy) on the CIFAR-10 benchmark, as well as commensurate energy savings on all standard tinyML application benchmarks. The key is enabling fully unrolled and pipelined operations which reduces the activation memory needed and eliminates hardware, and reduces activation access. (2810.078, B. Murmann, Stanford University) |

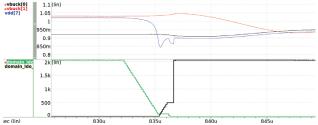

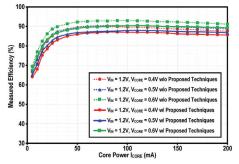

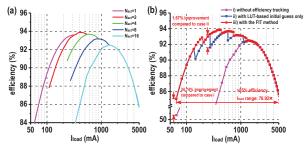

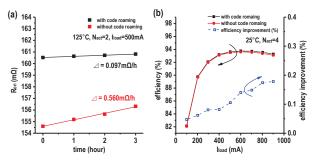

| Energy<br>Efficiency<br>(Circuits) | Efficiency of power delivery from high-voltage busses to scaled-CMOS-<br>compatible voltages (<1V) is improved by ~10% employing a vertically and<br>heterogeneously integrated architecture leveraging hybrid and switched-<br>capacitor DC-DC converters. This architecture also reduces the number of power<br>pins by at least 2x. The SCVR was implemented in a 65-nm CMOS process, while<br>the HVRM in a 180-nm BCD process. (2810.061, H. Le, UCSD)                                                                                                                                                                                          |

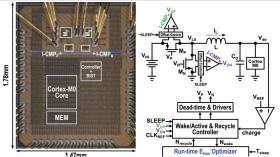

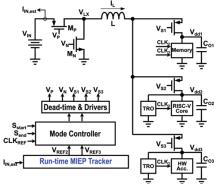

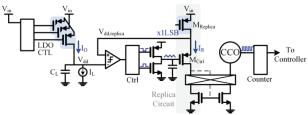

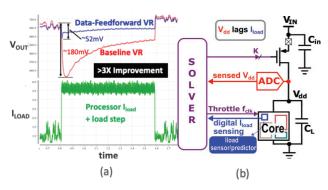

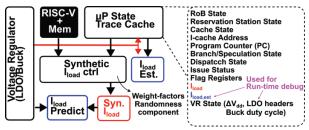

| Energy<br>Efficiency<br>(Circuits) | A linear regression machine learning model is trained based on simulation of both digital core and power management circuitry capturing the relationship among CPU's power consumption, supply droops, and CPU's internal signals, e.g. Opcode. A machine learning core generates a prediction of the CPU current consumption 2~3 cycles early, which is sent to the buck converter and combined with real-time measured supply voltage to deliver "feedforward" regulation to the incoming current surge. This proactive scheme achieves 6%~10% improvements on CPU frequency or converter efficiency. (2810.039, J. Gu, Northwestern Univ.)        |

|                                                      | A new EQCh/c multi-carrier transmitter (TV) has been developed utilizing carrier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

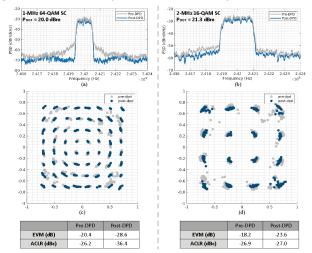

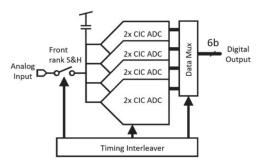

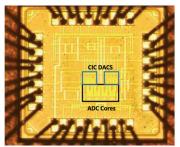

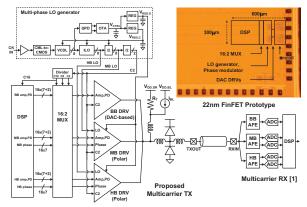

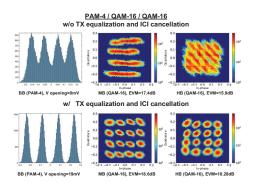

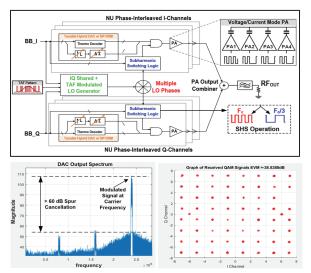

| Fundamental<br>Analog<br>(Circuits)                  | A new 50Gb/s multi-carrier transmitter (TX) has been developed, utilizing carrier orthogonality to allow band overlap. It features three 5GS/s bands with BB PAM4, MB, and HB 16-state complex modulation on carriers at 5 and 10GHz. The TX, fabricated in a 22-nm FinFET process, operates at 50Gb/s by activating these three bands simultaneously. The TX was used to demonstrates BER<10 <sup>-4</sup> over a channel with 5-dB loss at 12.5GHz, thanks to TX FIR equalization and 4-tap ICI cancellation. (2810.062, S. Palermo, Texas A&M University)                                                                                                                         |

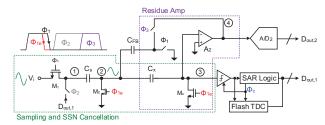

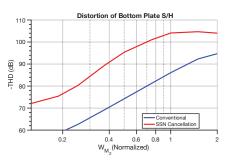

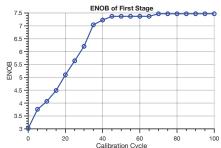

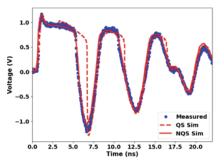

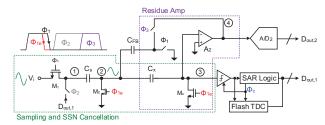

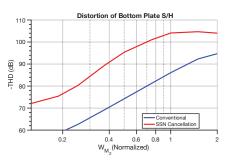

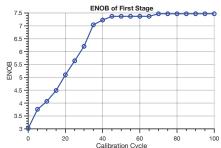

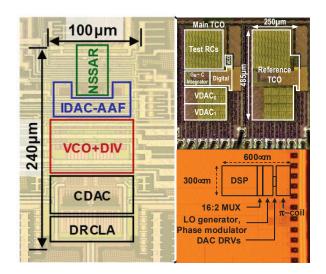

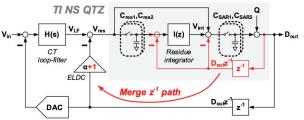

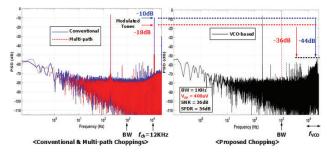

| Fundamental<br>Analog<br>(Circuits)                  | A new hybrid ADC architecture combines a VCO-based continuous-time delta-<br>sigma modulator (DSM) with a noise-shaping successive approximation register<br>(SAR) quantizer. The key innovation is an anti-aliasing filter (AAF) that connects<br>the VCO front-end with the NS-SAR quantizer, allowing direct sampling of time-<br>domain information as voltage-domain information. A 28-nm CMOS prototype<br>achieves an 84.2-dB signal-to-noise-distortion ratio and an 86.8-dB dynamic range<br>within a 1-MHz bandwidth while consuming 1.62mW at 100MS/s. The Schreier<br>SNDR figure of merit is 172.1 dB. (2810.033, M. Flynn, U. Michigan)                                |

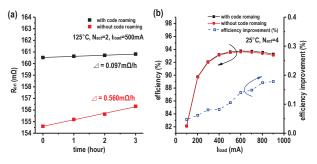

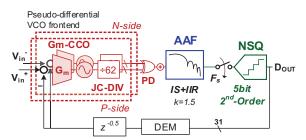

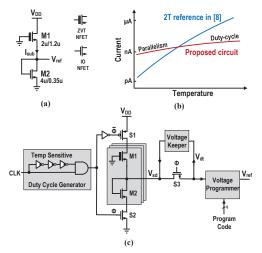

| Fundamental<br>Analog<br>(Circuits)                  | The first temperature- and aging-compensated RC Oscillator (TACO) maintains<br>long-term stability by periodically synchronizing its frequency with a less-aged<br>reference oscillator. To enhance its stability, TACO incorporates resistors with<br>higher activation energy ( $E_a$ ), employs switched dual RC branches to reduce stress<br>induced by DC currents, and applies duty cycling to slow down the aging of the<br>reference oscillator. A prototype 100-MHz oscillator built using a 65-nm CMOS<br>process achieves an inaccuracy of ±1030 ppm over -40°C to 85°C after 500 hours<br>of accelerated aging at 125°C. (2810.036, P. Hanumolu, University of Illinois) |

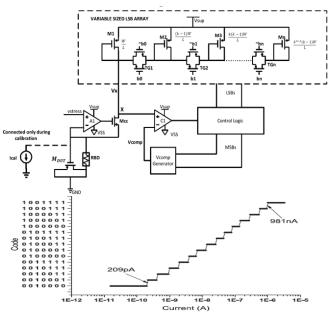

| Safety,<br>Security and<br>Health Care<br>(CADT)     | A cost-effective DfT (Design for Testing) method for improving LRFS (Lifetime<br>Reliability and Functional Safety) of analog and mixed-signal circuits has been<br>demonstrated. A concurrent sampling strategy was developed for simultaneous<br>multi-analog-node online measurements. The method was incorporated with a<br>digital-like DfT method and implemented with a PCB demo design. Low-cost SAR<br>ADC defect-oriented test achieved 100% defect coverage by re-using existing<br>digital circuitry. (2810.047, D. Chen, U of Iowa)                                                                                                                                     |

| Safety,<br>Security and<br>Health Care<br>(Circuits) | Miniaturized mid-infrared (IR) sensors operating at room temperature based on<br>ultrathin meta-surfaces integrated within a piezoelectric nanomechanical<br>resonator system (MEMS), optimized for gas sensing are demonstrated.<br>Outstanding NEP (noise equivalent power) of 80pW/VHz at room temperature,<br>drastically outperforming the state-of-the-art is achieved. (2810.050, S. Gomez<br>Diaz, UC Davis)                                                                                                                                                                                                                                                                 |

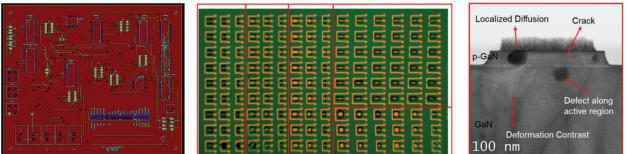

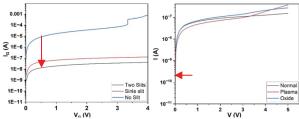

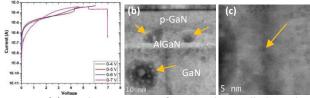

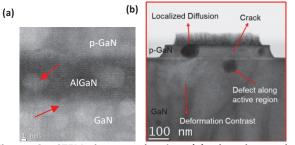

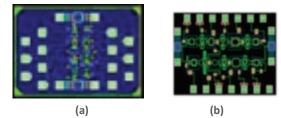

| Safety,<br>Security and<br>Health Care<br>(Circuits) | STEM images of commercially available p-GaN E-mode HEMTs are captured with<br>in-situ bias for electrical stress. The samples with a gate-drain structure were<br>prepared using FIB and e-chip. Leakage current was reduced using plasma and FIB<br>oxide deposition on the samples. This demonstration suggests a potential path<br>for identification of location of initial device failure, and understanding the gate's<br>multi-stage breakdown paths and the current evolution stages. (2810.057, M.<br>Kim, UT Dallas)                                                                                                                                                       |

## Safety, Security and Health Care Thrust

| Category                                             | Accomplishment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Safety,<br>Security and<br>Health Care<br>(CADT)     | A cost-effective DfT (Design for Testing) method for improving LRFS (Lifetime<br>Reliability and Functional Safety) of analog and mixed-signal circuits has been<br>demonstrated. A concurrent sampling strategy was developed for simultaneous<br>multi-analog-node online measurements. The method was incorporated with a<br>digital-like DfT method and implemented with a PCB demo design. Low-cost SAR<br>ADC defect-oriented test achieved 100% defect coverage by re-using existing<br>digital circuitry. (2810.047, D. Chen, U of Iowa) |  |

| Safety,<br>Security and<br>Health Care<br>(Systems)  | Miniaturized mid-infrared (IR) sensors operating at room temperature based on ultrathin meta-surfaces integrated within a piezoelectric nanomechanical resonator system (MEMS), optimized for gas sensing are demonstrated. Thousands of such sensors were tested to characterize their responsivity and noise. Outstanding NEP (noise equivalent power) of 80pW/vHz at room temperature, drastically outperforming the state-of-the-art is achieved. (2810.050, S. Gomez Diaz, UC Davis)                                                        |  |

| Safety,<br>Security and<br>Health Care<br>(Circuits) | STEM images of commercially available p-GaN E-mode HEMTs are captured with<br>in-situ bias for electrical stress. The samples with a gate-drain structure were<br>prepared using FIB and e-chip. Leakage current was reduced using plasma and FIB<br>oxide deposition on the samples. This demonstration suggests a potential path for<br>identification of location of initial device failure, and understanding the gate's<br>multi-stage breakdown paths and the current evolution stages. (2810.057, M. Kim,<br>UT Dallas)                   |  |

### TASK 2810.038, EXTREME TEMPERATURE DIGITAL, ANALOG, AND MIXED-SIGNAL CIRCUITS (ET-DAMS)

CHRIS H. KIM, UNIVERSITY OF MINNESOTA, CHRISKIM@UMN.EDU

### SIGNIFICANCE AND OBJECTIVES

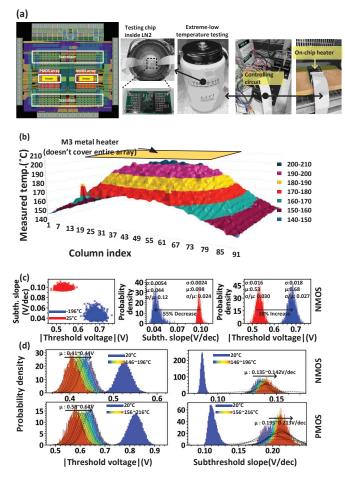

We have been focusing on the testing of the arraybased, densely populated transistor characterization circuit in a 0.35- $\mu$ m process. Using an on-chip heater and M1 metal-based temperature sensor, we were able to collect statistical IV curve data from a large number of devices from cryogenic conditions (liquid nitrogen, -196°C) as well as above 200°C, covering a wide temperature range.

### **TECHNICAL APPROACH**

Testing software was developed for an array-based characterization circuit to efficiently transistor characterize transistor I-V behavior under extreme temperatures. We have implemented a metal-based, small-sized on-chip heater to help us reach the target temperature using joule-heating for measurements above 200°C. We have also developed a robust cryogenic measurement system with enhanced connection for the measurement at 77K. In the past year, we have successfully collected I-V characteristics from 6 test chips. Each chip has over 12,000 transistors. The measurements were performed in both extremely high and extremely low temperatures.

### SUMMARY OF RESULTS

Fig. 1 shows the major results we have had in the past year. Fig. 1(a) shows the full chip layout of the 0.35-µm test chip with PMOS/NMOS array, on-chip-heaters, and scan-chain controlling circuitry. The rest of the top figure shows the extreme temperature measurement setup. For cryogenic measurements, we submerge the testing PCB inside a dewar of liquid nitrogen. All the connection points have been enhanced accordingly to prevent connection failure under cryogenic connections. Fig. 1(b) shows the temperature map for high-temperature measurements obtained by the threshold voltage measurements of each transistor in the device array. Figs. 1(c) and 1(d) show the characterization results of the transistor array under different temperatures including extremely high temperatures, room temperature, and 77K. The sigma/mu values of the subthreshold slope and threshold voltage distributions were 5X and 0.9x, respectively, at 77K as compared to 25°C. In Fig. 1(d), we have shown the distribution of transistor  $V_{TH}$  and subthreshold slope for temperatures ranging from 25°C to 216°C.

Figure 1. (a) Full chip layout of 0.350-µm device characterization array and measurement setup (b) Deviceunder-test temperature underneath the heater showing spatial gradient. (c) Variation measurements of NMOS transistors under 77K. (d) Variation measurements of NMOS and PMOS

transistors under temperature ranges from 146°C to 216°C.

**Keywords:** Device characterization array, on-chip heater, high temperature operation, cryogenic, fully automated testing

### INDUSTRY INTERACTIONS

Intel, Texas Instruments

### MAJOR PAPERS/PATENTS

[1] H. Yu, Y. Yi, N. Pande, and C.H. Kim, "On-chip Heater Design and Control Methodology for Reliability Testing Applications Requiring over 300°C Local Temperatures," IEEE Trans. Device and Material Reliability (TDMR), 2023.

### TASK 2810.041, ESD PROTECTION FOR IO OPERATING AT 56 GB/S AND BEYOND

ELYSE ROSENBAUM, UNIVERSITY OF ILLINOIS AT URBANA-CHAMPAIGN, ELYSE@ILLINOIS.EDU

#### SIGNIFICANCE AND OBJECTIVES

The project objective is to develop a co-design methodology for ESD-protected high-speed receiver front-end circuits. This will enable a designer to achieve adequate component-level ESD protection while also meeting return loss specifications.

### **TECHNICAL APPROACH**

Front-end circuits are co-designed for performance and ESD reliability. First, ESD hazards arising from a variety of bandwidth extension techniques are identified. Then, we identify the value  $V_{MAX}$ , which is the maximum tolerable voltage at the IO pin under ESD conditions. Next, the available protection devices are characterized using the metrics  $I_{fail}$ /Capacitance and  $R_{on}$ ·Capacitance. Finally, the performance and reliability of each candidate circuit are optimized through co-design.

### SUMMARY OF RESULTS

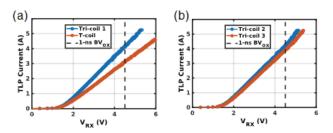

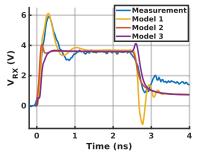

As reported last year, we developed distributed ESD protection by utilizing the parasitic resistance of a bandwidth extension circuit composed of 3 coupled inductors. The objective is to reduce the ESD-induced gate voltage applied to a wireline receiver's input transistors. The 3-inductor bandwidth extension circuit was named a tri-coil, to distinguish it from the pi-coil circuits that are placed at output pins. Recently, a 65-nm test chip was fabricated and tested. The test chip contains 3 tri-coils with integrated distributed ESD protection. The ESD diodes integrated into tri-coil 1 have a total width of 140  $\mu$ m, those in tri-coil 2 have a total width of 116  $\mu$ m, and those in tri-coil 3 have a total width of 93 µm. For benchmarking purposes, the test chip also contains a Tcoil with non-distributed ESD protection. The width of the ESD diode in the T-coil circuit is 140 µm that is the same as for tri-coil 1. Measurement results in Fig. 1 confirm that the tri-coil with distributed protection provides better voltage clamping than the conventional input circuit using a T-coil. The return loss and bandwidth of the tri-coil and T-coil based input circuits are similar [1], demonstrating that improved ESD reliability can be obtained without sacrificing performance.

An ESD protection circuit is designed to sink HBM current without suffering thermal damage and to limit the CDM-induced voltage below the breakdown voltage of the circuit being protected. It is desired that the protection device sizes, and the associated loading, are the smallest that can meet the protection targets. Dielectric

Figure 1. Pulse I-V of (a) tri-coil 1 and T-coil, and (b) tri-coil 2 and tri-coil 3. 2.5-ns pulse-width, 100 ps risetime. BVOX is the foundry-reported oxide breakdown voltage on a 1-ns time-scale.

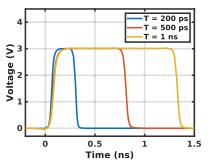

breakdown voltage increases with decreasing stress time. Therefore, to optimally size the ESD protection, it is necessary to know the transistor gate dielectric breakdown voltage on the CDM time scale. During CDM, the voltage is near its maximum value for just a few hundred ps. MOS test structures with integrated singleshot sub-1-ns pulse generators have been designed and are undergoing fabrication. In simulation, the pulses are near-ideal square pulses, unlike those produced by a TLP tester (Fig. 2). Our team recognized that a high-power pulse generator is not needed to induce oxide breakdown. Consequently, we use on-chip logic circuits to generate the square pulse. The chip is powered on only briefly, to avoid prolonged stress on the logic circuits.

Figure 2. Post layout simulation of pulses applied to MOS victim devices in 65-nm CMOS. Pulses of progressively higher amplitude are applied until the victim breaks down.

**Keywords:** ESD, CDM, impedance matching circuit, timedependent dielectric breakdown

### INDUSTRY INTERACTIONS

AMD, Texas Instruments

#### MAJOR PAPERS/PATENTS

[1] M. Drallmeier, et. al., "Distributed protection for...," to appear in 2023 EOS/ESD Symposium Proceedings.

### SIGNIFICANCE AND OBJECTIVES

We focus on electromigration (EM) failures in the onchip power grid and are developing tools to guarantee chip robustness in the face of EM degradation. Our goal is to provide techniques by which one can ensure EM reliability-by-design. The key advantage is improved accuracy and reduced conservatism.

### **TECHNICAL APPROACH**

It is difficult to achieve EM sign-off on modern chip designs, due to the limitations of traditional empirical models that are built into existing tools. Modern physical EM models allow one to overcome these limitations, but are expensive to use, especially when doing EM simulation on large chip power grids. Instead of simulation, we will develop an "inverse approach": generate design-aware constraints on the circuit currents which, if guaranteed during chip design, would ensure EM safety for the desired lifetime. Since these constraints correspond to the specific design, this has the potential to improve accuracy and reduce pessimism.

#### SUMMARY OF RESULTS

Under previous tasks, using the Korhonen stress-based model for EM (1993), we developed a linear (LTI) system model that describes the time-evolution of the stress vector as a function of line currents. We also used this to build a simulation engine for tracking the evolution of EM over time - the first practical *electromigration simulator*.

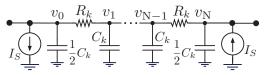

In 2021, we discovered that the relations between stress and flux in every interconnect tree metal line are identical to those between voltage and current in a specially designed electrical circuit (an RC network), as shown in Fig. 1. We call this an *equivalent circuit*, and it can be easily and automatically built for any given metal interconnect tree. If we solve the voltage-current problem for the equivalent circuit, then we have automatically solved the stress-flux problem for the interconnect tree. Node voltages in the equivalent circuit give the stresses in the metal network.

Figure 1. The equivalent circuit for a metal line.

We have used this equivalent circuit model to discover the closed-form analytical expression for the stress at all points in the interconnect tree for any given time t, in terms of the source currents applied to the tree, as

$\sigma(t) = e^{At}\sigma_0 + (I - e^{At})G^+ HMDM^+ i.$ This allows us to express the set (space) of safe DC current vectors that may be applied to the tree without violating the desired lifetime T for the tree, as captured by

$(I - e^{AT})G^+ HMDM^+ i \le \sigma_{crit} - e^{At}\sigma_0.$ The matrix that multiplies *i* on the left-hand-side in the above is what we call the *K* matrix. The computation of the matrix exponential  $e^{AT}$  is a very expensive, and the eigenvalues of the system matrix A are key to an efficient computation of the exponential. Empirical tests indicate that finding and using only the smallest eigenvalues is sufficient for accuracy. We have adapted the well-known Arnoldi algorithm, along with a shift-and-invert strategy, to generate approximations to the *k* smallest eigenvalues of the system matrix. This makes use of a projection of the full system matrix onto a smaller subspace based on the *k* smallest eigenvalues. Effectively, we are making use of an approximation by projection, as:

$$e^{At} \approx \tilde{Q} e^{\tilde{H}t} \tilde{Q}^*,$$

where  $\tilde{Q}$  and  $\tilde{H}$  are matrices generated by the algorithm, and  $\tilde{Q}^*$  is the complex conjugate transpose of  $\tilde{Q}$ . The  $\tilde{H}$ matrix is of much smaller size, and its exponential can be found more efficiently. Results show good accuracy, as shown by the normalized errors for the K matrix:

Table 1. Error results for a few test cases.

| # Junctions | RMS Error | Max Error | Average Error |

|-------------|-----------|-----------|---------------|

| 300         | 0.0577 %  | 0.3736 %  | 0.0410 %      |

| 700         | 0.3138 %  | 4.1548 %  | 0.1866 %      |

| 1,500       | 1.1444 %  | 27.459 %  | 0.5182 %      |

As for the runtimes, while MATLAB cannot compute the exponential for more than 1500 junctions, we are able to compute it for a grid with 5500 junctions, in 19 hours.

**Keywords:** integrated circuits, electromigration, stress, reliability, current constraints

#### INDUSTRY INTERACTIONS

NXP, Intel, Texas Instruments, Siemens

#### MAJOR PAPERS/PATENTS

[1] Shahriari & Najm, "Fast Sim...", in ISQED-2023.

### TASK 2810.047, ARCHITECTURE AND DFT METHODS FOR IMPROVING LIFETIME RELIABILITY AND FUNCTIONAL SAFETY DEGANG CHEN, IOWA STATE UNIVERSITY, DJCHEN@IASTATE.EDU

### SIGNIFICANCE AND OBJECTIVES

Increasingly more ICs are deployed in mission-critical applications to improve performance, reduce accidents, and save lives. Stringent requirements on lifetime reliability and functional safety (LRFS) are imposed but methodologies are significantly lagging for analog circuits. This project develops cost-effective DfT methods for greatly improving LRFS for analog and mixed-signal circuits.

### **TECHNICAL APPROACH**

We will develop a DfT (Design for Test) architecture and multilevel monitoring and healing solutions to ensure lifetime reliability and functional safety. Digital DfT is assumed available to check our circuits. At power-on, we will use digital-like controls and detectors to verify all analog connectivity and topological correctness, which ensures the functionality of basic analog components. With intrinsic process matching, we then perform accurate AMS BIST and calibration. After that, various health and aging monitors will go online. A concurrent sampling strategy will enable simultaneous measurements of many health and safety conditions and will trigger recalibration and/or safety actions as necessary.

### SUMMARY OF RESULTS

Recently, we began testing the wide-range temperature to digital converter and the built-in NBTI monitor. We demonstrated the proposed DfT methods through PCB measurements and simulations. We demonstrated the proposed simultaneous self-test and self-calibration of both ADC and DAC.

Over the course of this research, we applied the DfT method to a standard LDO defect detection. A wide-range temperature-to-digital converter design not requiring device model details was presented at ISCAS. SRC filed a patent for the design. We developed a digital strategy for checking all component connectivity inside a CDAC based SAR ADC, achieving structural test, defect detection, and defect localization. We developed a fast-sensing method for multi-device NBTI aging detection and completed a test-chip design and fabrication.

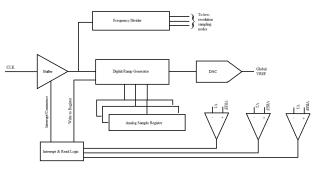

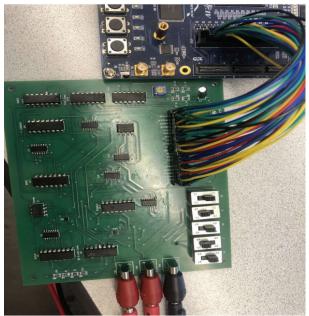

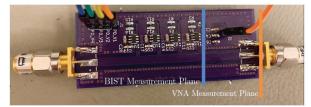

The high-resolution concurrent sampling strategy for AMS reliability and safety improvement is shown in Fig. 1. The strategy was demonstrated via PCB design and measurement as shown in Fig. 2.

Figure 1. High-resolution concurrent sampling method.

Figure 2. Analog test PCB and FPGA board for injecting analog faults and validating BISTs.

**Keywords:** lifetime reliability and functional safety, power-on AMS BIST, concurrent sampling

### INDUSTRY INTERACTIONS

Intel, MediaTek, NXP, Siemens, Texas Instruments

- [1] Kushagra Bhatheja, et al, 2022 ITC

- [2] Kushagra Bhatheja, et al, 2022 IEEE ISCAS

- [3] Mona Ganji, et al, 2022 IEEE ISCAS

- [4] Marampally Saikiran, et al, 2022 IEEE ISCAS

- [5] Kwabena Banahene, et al, 2022 IEEE ISCAS

- [6] Marampally Saikiran, et al, 2022 SBCCI

- [7] Marampally Saikiran, et al, 2022 SBCCI

- [8] Mona Ganji, et al, US Patent App. No. 18/095,853

### TASK 2810.048, CHARACTERIZATION AND MITIGATION OF ELECTROMIGRATION EFFECTS IN ADVANCED TECHNOLOGY NODES CHRIS H. KIM, UNIVERSITY OF MINNESOTA, CHRISKIM@UMN.EDU

### SIGNIFICANCE AND OBJECTIVES

Even though accurate Electromigration (EM) models are important for designing reliable chips, only limited silicon data has been reported due to difficulties of wellcalibrated experiments. In this project, EM failure trends and statistics will be collected from a dedicate power grid EM test chip using an automated testing setup.

### **TECHNICAL APPROACH**

Our test will focus on experiments on four different power grid structures fabricated on a single die leveraging circuit-based data collection. The four EM lifetimes and IR drop aggravation trends will be analyzed and compared with EM simulation models.

### SUMMARY OF RESULTS

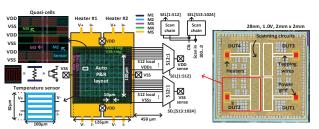

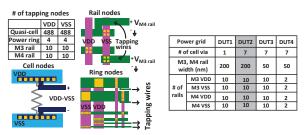

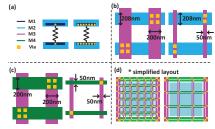

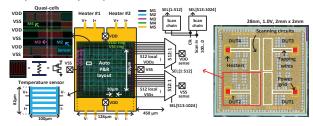

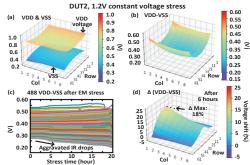

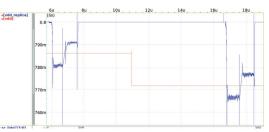

The experiment will be done on 28-nm power grid test chips. Using voltage scanning circuits that can measure 1024 internal voltage in the grid, allows the recording of  $V_{\text{DD}}$  and GND changes after EM stress for the failure analysis. As shown in Fig. 1, four different DUTs are designed to compare the failure behaviors. Each DUT is a realistic power grid with equivalent guasi-loads, and the DUT temperatures are accurately controlled by a dedicated temperature sensor. Fig. 2 and Fig. 3 show the rail width, cell via count, and rail density differences between the grids. Since we have various test structures and voltage tapping capabilities, we expect to find the dependency between the grid design and the failure time/location. Also, utilizing this Silicon data, the statistics will be used to calibrate the physics-based EM simulation models. For accurate data collection for EM experiments, controlling DUT temperature for consistent stress conditions is critical. To this end, we came up with a multithreaded test program to collect the data only under the stable DUT temperature (Fig. 4 (left)). By using this approach, EM failure statistics, which are sensitive to temperature, could be analyzed under the same stress conditions (Fig. 4 (right)). This experiment is a huge improvement compared to the previous ones since the heater control is no longer affected by the Joule heating of the DUT and the chip's process variation thanks to the dedicated sensor and the test software.

Figure 1. EM test chip overview for realistic power grid structures.

Figure 3. Cell via count, power rail width, and power rail density differences between the power grids.

Figure 4. Multi-threaded test flow (left) and on-chip heater control log for maintaining accurate DUT temperature (right).

**Keywords:** Electromigration, power grid, lifetime, characterization, test structure

### INDUSTRY INTERACTIONS

Intel, NXP, Siemens, Texas Instruments

### TASK 2810.050, INTEGRATING METASURFACES AND MEMS FOR GAS SENSING

SEBASTIAN GÓMEZ DÍAZ, UNIVERSITY OF CALIFORNIA AT DAVIS, JSGOMEZ@UCDAVIS.EDU

### SIGNIFICANCE AND OBJECTIVES

The goal is to demonstrate infrared (IR) sensors operating at room temperature based on metasurfaces (MTSs) integrated within a nanomechanical resonator system (NMEMS) with application in gas sensing. Experimental data demonstrate a noise equivalent power (NEP) of ~80 pW/ $\sqrt{\text{Hz}}$ , which is state-of-the-art for spectrally selective IR sensing.

### **TECHNICAL APPROACH**

tailored and By merging electromagnetic electromechanical resonances, miniaturized and fast IR detectors operating at room temperature have been demonstrated. The selectivity of the IR absorption is improved by optimizing the nanoresonators that compose the metasurface decorating the MEMS, showing absorption with a full-width half maximum below 0.2 um. The MEMSs are based on lateral contour modes, and exhibit quality factors above 2500 at ~200 MHz. Next, dozens of devices will be integrated within a chip to demonstrate a complete gas sensing system. To do this, each NMEMS will be tailored to an IR spectral fingerprint of the targeted gas.

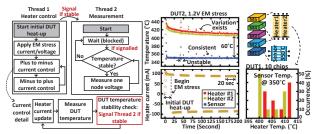

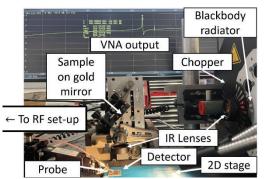

### SUMMARY OF RESULTS

In collaboration with Texas Instruments, we have designed, fabricated, and tested thousands of spectrally selective IR sensors based on NMEMS decorated with ultrathin metasurfaces (Fig. 1). We also developed an automatized electrical-infrared test bench to characterize the response of hundreds of sensors in terms of responsivity and noise (Fig. 2). The system is composed of a blackbody radiator, chopper, lenses, motorized vacuum choke stage, microscope, and probe station – all automatized through a dedicated MATLAB software.

Measured data permits correlating device geometry and performance, and in turn, develops design guidelines. Best detectors exhibit NEP of ~  $80 \text{ pW}/\sqrt{\text{Hz}}$  at room temperature, greatly surpassing the state of the art of this technology and opening exciting possibilities in the field of IR sensing.

Figure 1. (Top) Example of a spectrally-selective IR sensor. Top inset details the MEMS anchors. Central inset shows the metasurface pattern. (Bottom left) RF response of the device, demonstrating quality factors over 2700. (Bottom right) IR absorption of MEMS devices loaded with different metasurfaces. Inset shows SEM image of the fabricated device (left) and metasurfaces (right).

Figure 2. Experimental set-up to measure the responsivity and noise equivalent power of the proposed IR detector.

## **Keywords:** NMEMS, ultrathin metasurfaces, IR sensors, gas sensing, AIN resonators

### INDUSTRY INTERACTIONS

**Texas Instruments**

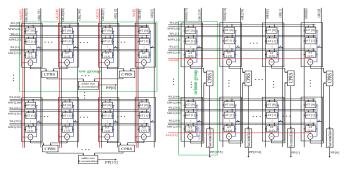

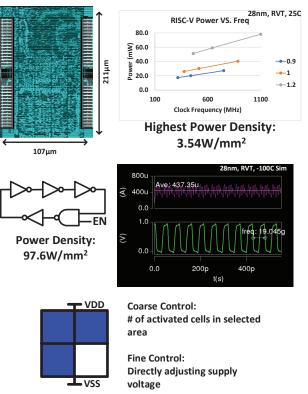

### TASK 2810.054, RECONFIGURABLE AC POWER CYCLING SETUP AND PLUG-IN CONDITION MONITORING TOOLS FOR HIGH POWER IGBT AND SIC MODULES

BILAL AKIN, UNIVERSITY OF TEXAS AT DALLAS, BILAL.AKIN@UTDALLAS.EDU

### SIGNIFICANCE AND OBJECTIVES

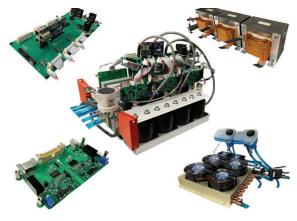

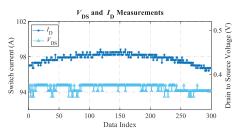

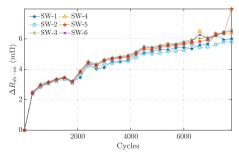

The long-term reliability of SiC MOSFET is a concern limiting its wide application. This study investigates the performance change in the SiC MOSFETs over aging through AC power cycling. The precursors are identified and condition monitoring circuits, lifetime models, and remaining useful lifetime estimation tools are developed accordingly.

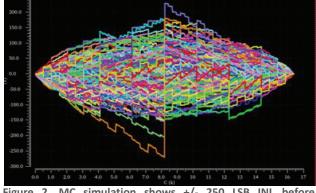

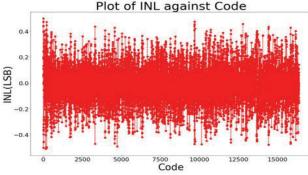

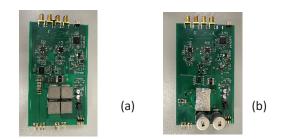

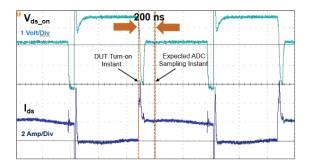

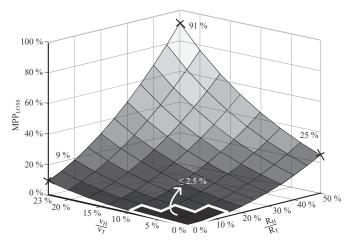

### **TECHNICAL APPROACH**